Microcontrollers

Never stop thinking.

#### **Edition 2001-03**

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany © Infineon Technologies AG 2001. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# Instruction Set Manual

for the C166 Family of Infineon 16-Bit Single-Chip Microcontrollers

# Microcontrollers

| C166 Family Microconti | C166 Family Microcontroller Instruction Set Manual |  |  |  |  |

|------------------------|----------------------------------------------------|--|--|--|--|

| Revision History:      | V2.0, 2001-03                                      |  |  |  |  |

| Previous Version:      | Version 1.2, 12.97                                 |  |  |  |  |

Version 1.1, 09-95 03.94

| Page         | Subjects (major changes since last revision)             |

|--------------|----------------------------------------------------------|

| all          | Converted to new company layout                          |

| 4 30         | Overview- and summary-tables reformatted                 |

| 2            | List of derivatives updated                              |

| 31           | Description template added                               |

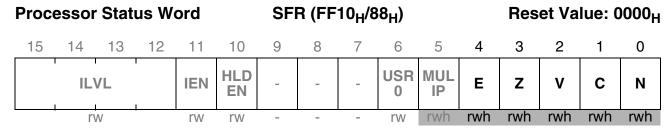

| 34           | PSW image added                                          |

| 38           | Condition code table moved                               |

| 40           | Note for MUL/DIV added                                   |

| <b>42</b> ff | Immediate data for byte instructions corrected to #data8 |

| <b>52</b> f  | Note improved                                            |

| 62           | Description of operation corrected                       |

| <b>72</b> ff | Description of division instructions improved            |

| 85           | Format description corrected                             |

| 86           | Description improved                                     |

| 101f         | Description of multiplication instructions improved      |

| 128          | Description of flags corrected                           |

| 132          | "bitoff" for ESFRs added                                 |

| 137          | Section moved                                            |

| 139          | Target address for "rel" corrected                       |

| 141          | General description improved                             |

| 142ff        | Timing examples converted to 25 MHz                      |

| 143          | Branch execution times corrected                         |

| <b>148</b> f | Keyword index introduced                                 |

|              |                                                          |

#### **We Listen to Your Comments**

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

| Table                                              | of Contents P                                                                                                                                                                                          | age                                    |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1                                                  | Introduction                                                                                                                                                                                           | 1                                      |

| 2                                                  | Overviews                                                                                                                                                                                              | 3                                      |

| 3<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5               | Summary  Data Addressing Modes  Branch Target Addressing Modes  Multiply and Divide Operations  Extension Operations  Branch Condition Codes                                                           | 8<br>8<br>9                            |

| 4                                                  | Encoding                                                                                                                                                                                               | . 22                                   |

| 5                                                  | Detailed Description                                                                                                                                                                                   | . 31                                   |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7 | Addressing Modes Short Addressing Modes Long Addressing Mode Indirect Addressing Modes DPP Override Mechanism Constants within Instructions Instruction Range (#irang2) Branch Target Addressing Modes | 132<br>134<br>135<br>137<br>138<br>138 |

| <b>7</b><br>7.1<br>7.2<br>7.3                      | Instruction State Times Time Unit Definitions Minimum Execution Time Additional State Times                                                                                                            | 142<br>143                             |

| 8                                                  | Keyword Index                                                                                                                                                                                          | 148                                    |

User's Manual V2.0, 2001-03

Introduction

#### 1 Introduction

The Infineon C166 Family of 16-bit microcontrollers offers devices that provide various levels of peripheral performance and programmability. This allows to equip each specific application with the microcontroller that fits best to the required functionality and performance.

Still the Infineon family concept provides an easy path to upgrade existing applications or to climb the next level of performance in order to realize a subsequent more sophisticated design. Two major characteristics enable this upgrade path to save and reuse almost all of the engineering efforts that have been made for previous designs:

- · All family members are based on the same basic architecture

- All family members execute the same instructions (except for upgrades for new members)

The fact that all members execute basically the same instructions saves know-how with respect to the understanding of the controller itself and also with respect to the used tools (assembler, disassembler, compiler, etc.).

This instruction set manual provides an easy and direct access to the instructions of the Infineon 16-bit microcontrollers by listing them according to different criteria, and also unloads the technical manuals for the different devices from redundant information.

This manual also describes the different addressing mechanisms and the relation between the logical addresses used in a program and the resulting physical addresses. There is also information provided to calculate the execution time for specific instructions depending on the used address locations and also specific exceptions to the standard rules.

#### **Description Levels**

In the following sections the instructions are compiled according to different criteria in order to provide different levels of precision:

- Cross Reference Tables summarize all instructions in condensed tables

- The Instruction Set Summary groups the individual instructions into functional groups

- The Opcode Table references the instructions by their hexadecimal opcode

- The Instruction Description describes each instruction in full detail

#### Introduction

All instructions listed in this manual are executed by the following devices (new derivatives will be added to this list):

- C161K, C161O, C161PI

- C161CS, C161JC, C161JI

- C163

- C164CI, C164SI, C164CM, C164SM

- C165

- C167CR, C167SR

- C167CS

A few instructions (ATOMIC and EXTended instructions) have been added for these devices and are not recognized by the following devices from the first generation of 16-bit microcontrollers:

- SAB 80C166, SAB 80C166W

- SAB 83C166, SAB 83C166W

These differences are noted for each instruction, where applicable.

#### 2 Overviews

The following compressed cross-reference tables quickly identify a specific instruction and provide basic information about it.

Two ordering schemes are included:

- The hexadecimal opcode of a specific instruction can be quickly identified with the respective mnemonic using the first compressed cross-reference table.

- The mnemonics and addressing modes of the various instructions are listed in the second table. The table shows which addressing modes may be used with a specific instruction and also the instruction length depending on the selected addressing mode. This reference helps to optimize instruction sequences in terms of code size and/or execution time.

Both ordering schemes (hexadecimal opcode and mnemonic) are provided in more detailed lists in the following sections of this manual.

Note: The ATOMIC and EXTended instructions are not available in the SAB 8XC166(W) devices.

They are **marked** in the cross-reference table.

Table 1 Instruction Overview ordered by Hex-Code (lower half)

|            | 0x    | 1x    | 2x    | 3x    | 4x   | 5x   | 6x   | 7x    |

|------------|-------|-------|-------|-------|------|------|------|-------|

| х0         | ADD   | ADDC  | SUB   | SUBC  | CMP  | XOR  | AND  | OR    |

| <b>x</b> 1 | ADDB  | ADDCB | SUBB  | SUBCB | СМРВ | XORB | ANDB | ORB   |

| <b>x2</b>  | ADD   | ADDC  | SUB   | SUBC  | CMP  | XOR  | AND  | OR    |

| х3         | ADDB  | ADDCB | SUBB  | SUBCB | СМРВ | XORB | ANDB | ORB   |

| <b>x</b> 4 | ADD   | ADDC  | SUB   | SUBC  | I    | XOR  | AND  | OR    |

| <b>x</b> 5 | ADDB  | ADDCB | SUBB  | SUBCB | I    | XORB | ANDB | ORB   |

| х6         | ADD   | ADDC  | SUB   | SUBC  | CMP  | XOR  | AND  | OR    |

| <b>x7</b>  | ADDB  | ADDCB | SUBB  | SUBCB | СМРВ | XORB | ANDB | ORB   |

| <b>x8</b>  | ADD   | ADDC  | SUB   | SUBC  | CMP  | XOR  | AND  | OR    |

| <b>x</b> 9 | ADDB  | ADDCB | SUBB  | SUBCB | СМРВ | XORB | ANDB | ORB   |

| хA         | BFLDL | BFLDH | ВСМР  | BMOVN | BMOV | BOR  | BAND | BXOR  |

| хВ         | MUL   | MULU  | PRIOR |       | DIV  | DIVU | DIVL | DIVLU |

| хC         | ROL   | ROL   | ROR   | ROR   | SHL  | SHL  | SHR  | SHR   |

| хD         | JMPR  | JMPR  | JMPR  | JMPR  | JMPR | JMPR | JMPR | JMPR  |

| хE         | BCLR  | BCLR  | BCLR  | BCLR  | BCLR | BCLR | BCLR | BCLR  |

| хF         | BSET  | BSET  | BSET  | BSET  | BSET | BSET | BSET | BSET  |

Table 2 Instruction Overview ordered by Hex-Code (upper half)

|            | 8x    | 9x    | Ax     | Вх    | Сх    | Dx                 | Ex    | Fx   |

|------------|-------|-------|--------|-------|-------|--------------------|-------|------|

| х0         | CMPI1 | CMPI2 | CMPD1  | CMPD2 | MOVBZ | MOVBS              | MOV   | MOV  |

| <b>x1</b>  | NEG   | CPL   | NEGB   | CPLB  | _     | ATOMIC<br>EXTR     | MOVB  | MOVB |

| <b>x2</b>  | CMPI1 | CMPI2 | CMPD1  | CMPD2 | MOVBZ | MOVBS              | PCALL | MOV  |

| х3         | _     | _     | _      | I     | I     | _                  | -     | MOVB |

| <b>x</b> 4 | MOV   | MOV   | MOVB   | MOVB  | MOV   | MOV                | MOVB  | MOVB |

| <b>x</b> 5 | _     | _     | DISWDT | EINIT | MOVBZ | MOVBS              | -     | _    |

| х6         | CMPI1 | CMPI2 | CMPD1  | CMPD2 | SCXT  | SCXT               | MOV   | MOV  |

| <b>x</b> 7 | IDLE  | PWRDN | SRVWDT | SRST  | ı     | EXTP[R]<br>EXTS[R] | MOVB  | MOVB |

| <b>x8</b>  | MOV   | MOV   | MOV    | MOV   | MOV   | MOV                | MOV   | _    |

| <b>x9</b>  | MOVB  | MOVB  | MOVB   | MOVB  | MOVB  | MOVB               | MOVB  | _    |

| хA         | JB    | JNB   | JBC    | JNBS  | CALLA | CALLS              | JMPA  | JMPS |

| хВ         | _     | TRAP  | CALLI  | CALLR | RET   | RETS               | RETP  | RETI |

| хC         | _     | JMPI  | ASHR   | ASHR  | NOP   | EXTP[R]<br>EXTS[R] | PUSH  | POP  |

| хD         | JMPR  | JMPR  | JMPR   | JMPR  | JMPR  | JMPR               | JMPR  | JMPR |

| хE         | BCLR  | BCLR  | BCLR   | BCLR  | BCLR  | BCLR               | BCLR  | BCLR |

| хF         | BSET  | BSET  | BSET   | BSET  | BSET  | BSET               | BSET  | BSET |

Table 3 Instruction Overview ordered by Mnemonic

| Mnemo-<br>nic(s)                             | Addressing           | Modes                                     | Bytes | Mnemo-<br>nic(s)                                   | Addressing                           | Modes                                                            | Bytes                      |

|----------------------------------------------|----------------------|-------------------------------------------|-------|----------------------------------------------------|--------------------------------------|------------------------------------------------------------------|----------------------------|

| ADD[B]<br>ADDC[B]                            | Rwn,<br>Rwn,         | Rwm<br>[Rwi]                              | 2     | CPL[B]<br>NEG[B]                                   | Rwn (Rbn) <sup>1)</sup>              |                                                                  | 2                          |

| AND[B] OR[B] SUB[B] SUBC[B]                  | Rwn,<br>Rwn,<br>reg, | [Rwi+]<br>#data3<br>#data16 <sup>2)</sup> | 2 2 4 | DIV<br>DIVL<br>DIVLU<br>DIVU                       | Rwn                                  |                                                                  | 2                          |

| XOR[B] <sup>1)</sup>                         | reg,<br>mem,         | mem<br>reg                                | 4     | MUL<br>MULU                                        | Rwn,                                 | Rwm                                                              | 2                          |

| ASHR<br>ROL                                  | Rwn,<br>Rwn,         | Rwm<br>#data4                             | 2     | CMPD1<br>CMPD2                                     | Rwn,                                 | #data4                                                           | 2                          |

| ROR<br>SHL<br>SHR                            |                      |                                           |       | CMPI1<br>CMPI2                                     | Rwn,<br>Rwn,                         | #data16<br>mem                                                   | 4                          |

| BAND<br>BCMP<br>BMOV<br>BMOVN<br>BOR<br>BXOR | bitaddrZ.z,          | bitaddrQ.q                                | 4     | CMP<br>CMPB <sup>1)</sup>                          | Rwn,<br>Rwn,<br>Rwn,<br>reg,<br>reg, | Rwm<br>[Rwi]<br>[Rwi+]<br>#data3<br>#data16 <sup>2)</sup><br>mem | 2<br>2<br>2<br>2<br>4<br>4 |

| BCLR<br>BSET                                 | bitaddrQ.q           |                                           | 2     | CALLA<br>JMPA                                      | CC,                                  | caddr                                                            | 4                          |

| BFLDH<br>BFLDL                               | bitoffQ,             | #mask8,<br>#data8                         | 4     | CALLI<br>JMPI                                      | cc,                                  | [Rwn]                                                            | 2                          |

| EXTS<br>EXTSR                                | Rwm,<br>#seg,        | #irang2 <sup>3)</sup><br>#irang2          | 2     | EXTP<br>EXTPR                                      | Rwm,<br>#pag,                        | #irang2 <sup>3</sup><br>#irang2                                  | 2 4                        |

| NOP<br>RET<br>RETI<br>RETS                   | _                    |                                           | 2     | SRST<br>IDLE<br>PWRDN<br>SRVWDT<br>DISWDT<br>EINIT | _                                    |                                                                  | 4                          |

**Table 3** Instruction Overview ordered by Mnemonic (cont'd)

| Mnemo-<br>nic(s)          | Addressing                             | Modes                                    | Bytes            | Mnemo-<br>nic(s)         | Addressing  | Modes   | Bytes |

|---------------------------|----------------------------------------|------------------------------------------|------------------|--------------------------|-------------|---------|-------|

| MOV<br>MOVB <sup>1)</sup> | Rwn,<br>Rwn,                           | Rwm<br>#data4                            | 2                | CALLS<br>JMPS            | seg,        | caddr   | 4     |

|                           | Rwn,                                   | [Rwm]                                    | 2                | CALLR                    | rel         |         | 2     |

|                           | Rwn,<br>[Rwm],                         | [Rwm+]<br>Rwn                            | 2                | JMPR                     | CC,         | rel     | 2     |

|                           | [-Rwm],<br>[Rwn],<br>[Rwn+],<br>[Rwn], | Rwn<br>[Rwm]<br>[Rwm]<br>[Rwm+]          | 2 2 2            | JB<br>JBC<br>JNB<br>JNBS | bitaddrQ.q, | rel     | 4     |

|                           |                                        | "                                        |                  | PCALL                    | reg,        | caddr   | 4     |

|                           | reg,<br>Rwn,<br>[Rwm+#d16],<br>[Rwn],  | #data16 <sup>2)</sup> [Rwm+#d16] Rwn mem | 4<br>4<br>4<br>4 | POP<br>PUSH<br>RETP      | reg         |         | 2     |

|                           | mem,                                   | [Rwn]                                    | 4                | SCXT                     | reg,        | #data16 | 4     |

|                           | reg,                                   | mem                                      | 4                |                          | reg,        | mem     | 4     |

|                           | mem,                                   | reg                                      | 4                | PRIOR                    | Rwn,        | Rwm     | 2     |

| MOVBS                     | Rwn,                                   | Rbm                                      | 2                | TRAP                     | #trap7      |         | 2     |

| MOVBZ                     | reg,<br>mem,                           | mem<br>reg                               | 4                | ATOMIC<br>EXTR           | #irang2     | 3)      | 2     |

<sup>1)</sup> Byte oriented instructions (suffix 'B') use byte registers (Rb instead of Rw), except for indirect addressing modes ([Rw] or [Rw+]).

<sup>&</sup>lt;sup>2)</sup> Byte oriented instructions (suffix 'B') use #data8 instead of #data16.

<sup>3)</sup> The ATOMIC and EXTended instructions are not available in the SAB 8XC166(W) devices.

### 3 Summary

This chapter summarizes the instructions by listing them according to their functional class. This enables the user to identify the right instruction(s) for a specific required function.

The following general explanations apply to this summary:

#### 3.1 Data Addressing Modes

Rw: Word GPR (R0, R1, ..., R15)

Rb: Byte GPR (RL0, RH0, ..., RL7, RH7)

reg: SFR/ESFR or GPR

(in case of a byte operation on an SFR, only the low byte can be accessed

via 'reg')

mem: Direct word or byte memory location

[...]: Indirect word or byte memory location

(Any word GPR can be used as indirect address pointer, except for the arithmetic, logical and compare instructions, where only R0 to R3 are

allowed)

baddr: Direct bit in the bit-addressable memory area

bitoff: Direct word in the bit-addressable memory area

#datax: Immediate constant

(The number of significant bits which can be specified by the user is

represented by the respective appendix 'x')

#mask8: Immediate 8-bit mask used for bit-field modifications

#### 3.2 Branch Target Addressing Modes

caddr: Direct 16-bit jump target address (updates the Instruction Pointer)

Rb: Byte GPR (RL0, RH0, ..., RL7, RH7)

seg: Direct 8-bit segment address<sup>1)</sup>

(updates the Code Segment Pointer)

rel: Signed 8-bit jump target word offset address relative to the Instruction

Pointer of the following instruction

#trap7: Immediate 7-bit trap or interrupt number

<sup>1)</sup> In the 8XC166(W) devices the segment is only a 2-bit number, due to the smaller address range.

#### 3.3 Multiply and Divide Operations

The MDL and MDH registers are implicit source and/or destination operands of the multiply and divide instructions.

#### 3.4 Extension Operations

#pag10: Immediate 10-bit page address#seg8: Immediate 8-bit segment address#irang2: Immediate 2-bit instruction range

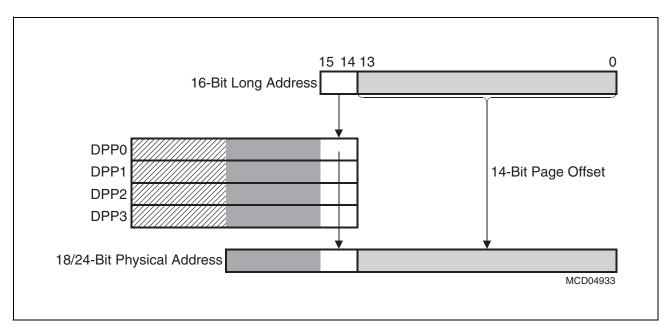

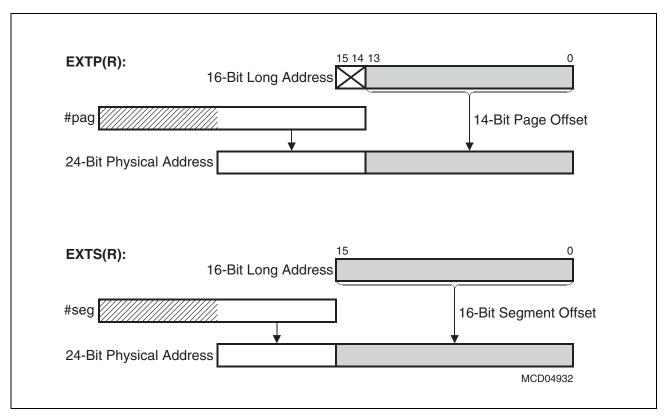

The extension instructions EXTP, EXTPR, EXTS, and EXTSR override the standard DPP addressing scheme, using immediate addresses instead.

Note: The EXTended instructions are not available in the SAB 8XC166(W) devices.

#### 3.5 Branch Condition Codes

| cc: | cc_UC  | Unconditional                  |

|-----|--------|--------------------------------|

|     | cc_Z   | Zero                           |

|     | cc_NZ  | Not Zero                       |

|     | cc_V   | Overflow                       |

|     | cc_NV  | No Overflow                    |

|     | cc_N   | Negative                       |

|     | cc_NN  | Not Negative                   |

|     | cc_C   | Carry                          |

|     | cc_NC  | No Carry                       |

|     | cc_EQ  | Equal                          |

|     | cc_NE  | Not Equal                      |

|     | cc_ULT | Unsigned Less Than             |

|     | cc_ULE | Unsigned Less Than or Equal    |

|     | cc_UGE | Unsigned Greater Than or Equal |

|     | cc_UGT | Unsigned Greater Than          |

|     | cc_SLE | Signed Less Than or Equal      |

|     | cc_SGE | Signed Greater Than or Equal   |

|     | cc_SGT | Signed Greater Than            |

|     | cc_NET | Not Equal and Not End-of-Table |

Note: Condition codes can be specified symbolically within an instruction.

A detailed description of the condition codes can be found in **Table 5**.

# Table 4 Instruction Set Summary

| Mnemonic |                | Description                                                                              |   |  |  |  |

|----------|----------------|------------------------------------------------------------------------------------------|---|--|--|--|

| Arithme  | tic Operations | 3                                                                                        |   |  |  |  |

| ADD      | Rw, Rw         | Add direct word GPR to direct GPR                                                        | 2 |  |  |  |

| ADD      | Rw, [Rw]       | Add indirect word memory to direct GPR                                                   | 2 |  |  |  |

| ADD      | Rw, [Rw+]      | Add indirect word memory to direct GPR and post-increment source pointer by 2            | 2 |  |  |  |

| ADD      | Rw, #data3     | Add immediate word data to direct GPR                                                    | 2 |  |  |  |

| ADD      | reg, #data16   | Add immediate word data to direct register                                               | 4 |  |  |  |

| ADD      | reg, mem       | Add direct word memory to direct register                                                | 4 |  |  |  |

| ADD      | mem, reg       | Add direct word register to direct memory                                                | 4 |  |  |  |

| ADDB     | Rb, Rb         | Add direct byte GPR to direct GPR                                                        | 2 |  |  |  |

| ADDB     | Rb, [Rw]       | Add indirect byte memory to direct GPR                                                   | 2 |  |  |  |

| ADDB     | Rb, [Rw+]      | Add indirect byte memory to direct GPR and post-increment source pointer by 1            | 2 |  |  |  |

| ADDB     | Rb, #data3     | Add immediate byte data to direct GPR                                                    | 2 |  |  |  |

| ADDB     | reg, #data8    | Add immediate byte data to direct register                                               | 4 |  |  |  |

| ADDB     | reg, mem       | Add direct byte memory to direct register                                                | 4 |  |  |  |

| ADDB     | mem, reg       | Add direct byte register to direct memory                                                | 4 |  |  |  |

| ADDC     | Rw, Rw         | Add direct word GPR to direct GPR with Carry                                             | 2 |  |  |  |

| ADDC     | Rw, [Rw]       | Add indirect word memory to direct GPR with Carry                                        | 2 |  |  |  |

| ADDC     | Rw, [Rw+]      | Add indirect word memory to direct GPR with Carry and post-increment source pointer by 2 | 2 |  |  |  |

| ADDC     | Rw, #data3     | Add immediate word data to direct GPR with Carry                                         | 2 |  |  |  |

| ADDC     | reg, #data16   | Add immediate word data to direct register with Carry                                    | 4 |  |  |  |

| ADDC     | reg, mem       | Add direct word memory to direct register with Carry                                     | 4 |  |  |  |

| ADDC     | mem, reg       | Add direct word register to direct memory with Carry                                     | 4 |  |  |  |

| ADDCB    | Rb, Rb         | Add direct byte GPR to direct GPR with Carry                                             | 2 |  |  |  |

| ADDCB    | Rb, [Rw]       | Add indirect byte memory to direct GPR with Carry                                        | 2 |  |  |  |

| ADDCB    | Rb, [Rw+]      | Add indirect byte memory to direct GPR with Carry and post-increment source pointer by 1 | 2 |  |  |  |

| ADDCB    | Rb, #data3     | Add immediate byte data to direct GPR with Carry                                         | 2 |  |  |  |

# Table 4 Instruction Set Summary (cont'd)

| Mnemonic |                | Description                                                                                     |   |  |  |  |

|----------|----------------|-------------------------------------------------------------------------------------------------|---|--|--|--|

| Arithme  | tic Operations | s (cont'd)                                                                                      |   |  |  |  |

| ADDCB    | reg, #data8    | Add immediate byte data to direct register with Carry                                           | 4 |  |  |  |

| ADDCB    | reg, mem       | Add direct byte memory to direct register with Carry                                            | 4 |  |  |  |

| ADDCB    | mem, reg       | Add direct byte register to direct memory with Carry                                            | 4 |  |  |  |

| SUB      | Rw, Rw         | Subtract direct word GPR from direct GPR                                                        | 2 |  |  |  |

| SUB      | Rw, [Rw]       | Subtract indirect word memory from direct GPR                                                   | 2 |  |  |  |

| SUB      | Rw, [Rw+]      | Subtract indirect word memory from direct GPR and post-increment source pointer by 2            | 2 |  |  |  |

| SUB      | Rw, #data3     | Subtract immediate word data from direct GPR                                                    | 2 |  |  |  |

| SUB      | reg, #data16   | Subtract immediate word data from direct register                                               | 4 |  |  |  |

| SUB      | reg, mem       | Subtract direct word memory from direct register                                                | 4 |  |  |  |

| SUB      | mem, reg       | Subtract direct word register from direct memory                                                | 4 |  |  |  |

| SUBB     | Rb, Rb         | Subtract direct byte GPR from direct GPR                                                        | 2 |  |  |  |

| SUBB     | Rb, [Rw]       | Subtract indirect byte memory from direct GPR                                                   | 2 |  |  |  |

| SUBB     | Rb, [Rw+]      | Subtract indirect byte memory from direct GPR and post-increment source pointer by 1            | 2 |  |  |  |

| SUBB     | Rb, #data3     | Subtract immediate byte data from direct GPR                                                    | 2 |  |  |  |

| SUBB     | reg, #data8    | Subtract immediate byte data from direct register                                               | 4 |  |  |  |

| SUBB     | reg, mem       | Subtract direct byte memory from direct register                                                | 4 |  |  |  |

| SUBB     | mem, reg       | Subtract direct byte register from direct memory                                                | 4 |  |  |  |

| SUBC     | Rw, Rw         | Subtract direct word GPR from direct GPR with Carry                                             | 2 |  |  |  |

| SUBC     | Rw, [Rw]       | Subtract indirect word memory from direct GPR with Carry                                        | 2 |  |  |  |

| SUBC     | Rw, [Rw+]      | Subtract indirect word memory from direct GPR with Carry and post-increment source pointer by 2 | 2 |  |  |  |

| SUBC     | Rw, #data3     | Subtract immediate word data from direct GPR with Carry                                         | 2 |  |  |  |

| SUBC     | reg, #data16   | Subtract immediate word data from direct register with Carry                                    | 4 |  |  |  |

| SUBC     | reg, mem       | Subtract direct word memory from direct register with Carry                                     | 4 |  |  |  |

Table 4 Instruction Set Summary (cont'd)

| Mnemo   | nic           | Description                                                                                     | Bytes |

|---------|---------------|-------------------------------------------------------------------------------------------------|-------|

| Arithme | tic Operation | s (cont'd)                                                                                      |       |

| SUBC    | mem, reg      | Subtract direct word register from direct memory with Carry                                     | 4     |

| SUBCB   | Rb, Rb        | Subtract direct byte GPR from direct GPR with Carry                                             | 2     |

| SUBCB   | Rb, [Rw]      | Subtract indirect byte memory from direct GPR with Carry                                        | 2     |

| SUBCB   | Rb, [Rw+]     | Subtract indirect byte memory from direct GPR with Carry and post-increment source pointer by 1 | 2     |

| SUBCB   | Rb, #data3    | Subtract immediate byte data from direct GPR with Carry                                         | 2     |

| SUBCB   | reg, #data8   | Subtract immediate byte data from direct register with Carry                                    | 4     |

| SUBCB   | reg, mem      | Subtract direct byte memory from direct register with Carry                                     | 4     |

| SUBCB   | mem, reg      | Subtract direct byte register from direct memory with Carry                                     | 4     |

| MUL     | Rw, Rw        | Signed multiply direct GPR by direct GPR (16-bit × 16-bit)                                      | 2     |

| MULU    | Rw, Rw        | Unsigned multiply direct GPR by direct GPR (16-bit × 16-bit)                                    | 2     |

| DIV     | Rw            | Signed divide register MDL by direct GPR (16-bit ÷ 16-bit)                                      | 2     |

| DIVL    | Rw            | Signed long divide register MD by direct GPR (32-bit ÷ 16-bit)                                  | 2     |

| DIVLU   | Rw            | Unsigned long divide register MD by direct GPR (32-bit ÷ 16-bit)                                | 2     |

| DIVU    | Rw            | Unsigned divide register MDL by direct GPR (16-bit ÷ 16-bit)                                    | 2     |

| CPL     | Rw            | Complement direct word GPR                                                                      | 2     |

| CPLB    | Rb            | Complement direct byte GPR                                                                      | 2     |

| NEG     | Rw            | Negate direct word GPR                                                                          | 2     |

| NEGB    | Rb            | Negate direct byte GPR                                                                          | 2     |

Table 4 Instruction Set Summary (cont'd)

| Mnemonic |              | Description                                                                             |   |  |  |

|----------|--------------|-----------------------------------------------------------------------------------------|---|--|--|

| Logical  | Instructions |                                                                                         |   |  |  |

| AND      | Rw, Rw       | Bitwise AND direct word GPR with direct GPR                                             | 2 |  |  |

| AND      | Rw, [Rw]     | Bitwise AND indirect word memory with direct GPR                                        | 2 |  |  |

| AND      | Rw, [Rw+]    | Bitwise AND indirect word memory with direct GPR and post-increment source pointer by 2 | 2 |  |  |

| AND      | Rw, #data3   | Bitwise AND immediate word data with direct GPR                                         | 2 |  |  |

| AND      | reg, #data16 | Bitwise AND immediate word data with direct register                                    | 4 |  |  |

| AND      | reg, mem     | Bitwise AND direct word memory with direct register                                     | 4 |  |  |

| AND      | mem, reg     | Bitwise AND direct word register with direct memory                                     | 4 |  |  |

| ANDB     | Rb, Rb       | Bitwise AND direct byte GPR with direct GPR                                             | 2 |  |  |

| ANDB     | Rb, [Rw]     | Bitwise AND indirect byte memory with direct GPR                                        | 2 |  |  |

| ANDB     | Rb, [Rw+]    | Bitwise AND indirect byte memory with direct GPR and post-increment source pointer by 1 | 2 |  |  |

| ANDB     | Rb, #data3   | Bitwise AND immediate byte data with direct GPR                                         | 2 |  |  |

| ANDB     | reg, #data8  | Bitwise AND immediate byte data with direct register                                    | 4 |  |  |

| ANDB     | reg, mem     | Bitwise AND direct byte memory with direct register                                     | 4 |  |  |

| ANDB     | mem, reg     | Bitwise AND direct byte register with direct memory                                     | 4 |  |  |

| OR       | Rw, Rw       | Bitwise OR direct word GPR with direct GPR                                              | 2 |  |  |

| OR       | Rw, [Rw]     | Bitwise OR indirect word memory with direct GPR                                         | 2 |  |  |

| OR       | Rw, [Rw+]    | Bitwise OR indirect word memory with direct GPR and post-increment source pointer by 2  | 2 |  |  |

| OR       | Rw, #data3   | Bitwise OR immediate word data with direct GPR                                          | 2 |  |  |

| OR       | reg, #data16 | Bitwise OR immediate word data with direct register                                     | 4 |  |  |

| OR       | reg, mem     | Bitwise OR direct word memory with direct register                                      | 4 |  |  |

| OR       | mem, reg     | Bitwise OR direct word register with direct memory                                      | 4 |  |  |

| ORB      | Rb, Rb       | Bitwise OR direct byte GPR with direct GPR                                              | 2 |  |  |

| ORB      | Rb, [Rw]     | Bitwise OR indirect byte memory with direct GPR                                         | 2 |  |  |

| ORB      | Rb, [Rw+]    | Bitwise OR indirect byte memory with direct GPR and post-increment source pointer by 1  | 2 |  |  |

| ORB      | Rb, #data3   | Bitwise OR immediate byte data with direct GPR                                          | 2 |  |  |

#### Table 4 Instruction Set Summary (cont'd)

| Mnemo                         | nic          | Description                                                                             | Bytes  |

|-------------------------------|--------------|-----------------------------------------------------------------------------------------|--------|

|                               |              | Boompton                                                                                | J, too |

| Logical Instructions (cont'd) |              |                                                                                         |        |

| ORB                           | reg, #data8  | Bitwise OR immediate byte data with direct register                                     | 4      |

| ORB                           | reg, mem     | Bitwise OR direct byte memory with direct register                                      | 4      |

| ORB                           | mem, reg     | Bitwise OR direct byte register with direct memory                                      | 4      |

| XOR                           | Rw, Rw       | Bitwise XOR direct word GPR with direct GPR                                             | 2      |

| XOR                           | Rw, [Rw]     | Bitwise XOR indirect word memory with direct GPR                                        | 2      |

| XOR                           | Rw, [Rw+]    | Bitwise XOR indirect word memory with direct GPR and post-increment source pointer by 2 | 2      |

| XOR                           | Rw, #data3   | Bitwise XOR immediate word data with direct GPR                                         | 2      |

| XOR                           | reg, #data16 | Bitwise XOR immediate word data with direct register                                    | 4      |

| XOR                           | reg, mem     | Bitwise XOR direct word memory with direct register                                     | 4      |

| XOR                           | mem, reg     | Bitwise XOR direct word register with direct memory                                     | 4      |

| XORB                          | Rb, Rb       | Bitwise XOR direct byte GPR with direct GPR                                             | 2      |

| XORB                          | Rb, [Rw]     | Bitwise XOR indirect byte memory with direct GPR                                        | 2      |

| XORB                          | Rb, [Rw+]    | Bitwise XOR indirect byte memory with direct GPR and post-increment source pointer by 1 | 2      |

| XORB                          | Rb, #data3   | Bitwise XOR immediate byte data with direct GPR                                         | 2      |

| XORB                          | reg, #data8  | Bitwise XOR immediate byte data with direct register                                    | 4      |

| XORB                          | reg, mem     | Bitwise XOR direct byte memory with direct register                                     | 4      |

| XORB                          | mem, reg     | Bitwise XOR direct byte register with direct memory                                     | 4      |

#### **Prioritize Instruction**

| PRIOR Rw, Rw | Determine number of shift cycles to normalize direct | 2 |

|--------------|------------------------------------------------------|---|

|              | word GPR and store result in direct word GPR         |   |

# Table 4 Instruction Set Summary (cont'd)

| Mnemonic         |                   | Description                                                                               |   |

|------------------|-------------------|-------------------------------------------------------------------------------------------|---|

| Boolear          | n Bit Manipula    | tion Operations                                                                           |   |

| BCLR             | baddr             | Clear direct bit                                                                          | 2 |

| BSET             | baddr             | Set direct bit                                                                            | 2 |

| BMOV             | baddr, baddr      | Move direct bit to direct bit                                                             | 4 |

| BMOVN            | baddr, baddr      | Move negated direct bit to direct bit                                                     | 4 |

| BAND             | baddr, baddr      | AND direct bit with direct bit                                                            | 4 |

| BOR              | baddr, baddr      | OR direct bit with direct bit                                                             | 4 |

| BXOR             | baddr, baddr      | XOR direct bit with direct bit                                                            | 4 |

| BCMP             | baddr, baddr      | Compare direct bit to direct bit                                                          | 4 |

| BFLDH<br>#mask8, | bitoff,<br>#data8 | Bitwise modify masked high byte of bit-addressable direct word memory with immediate data | 4 |

| BFLDL<br>#mask8, | bitoff,<br>#data8 | Bitwise modify masked low byte of bit-addressable direct word memory with immediate data  | 4 |

| CMP              | Rw, Rw            | Compare direct word GPR to direct GPR                                                     | 2 |

| CMP              | Rw, [Rw]          | Compare indirect word memory to direct GPR                                                | 2 |

| CMP              | Rw, [Rw+]         | Compare indirect word memory to direct GPR and post-increment source pointer by 2         | 2 |

| СМР              | Rw, #data3        | Compare immediate word data to direct GPR                                                 | 2 |

| CMP              | reg, #data16      | Compare immediate word data to direct register                                            | 4 |

| CMP              | reg, mem          | Compare direct word memory to direct register                                             | 4 |

| СМРВ             | Rb, Rb            | Compare direct byte GPR to direct GPR                                                     | 2 |

| СМРВ             | Rb, [Rw]          | Compare indirect byte memory to direct GPR                                                | 2 |

| СМРВ             | Rb, [Rw+]         | Compare indirect byte memory to direct GPR and post-increment source pointer by 1         | 2 |

| СМРВ             | Rb, #data3        | Compare immediate byte data to direct GPR                                                 | 2 |

| СМРВ             | reg, #data8       | Compare immediate byte data to direct register                                            | 4 |

| СМРВ             | reg, mem          | Compare direct byte memory to direct register                                             | 4 |

#### Table 4 Instruction Set Summary (cont'd)

| Mnemoi | nic          | Description                                                      | Bytes |

|--------|--------------|------------------------------------------------------------------|-------|

| Compar | e and Loop C | ontrol Instructions                                              |       |

| CMPD1  | Rw, #data4   | Compare immediate word data to direct GPR and decrement GPR by 1 | 2     |

| CMPD1  | Rw, #data16  | Compare immediate word data to direct GPR and decrement GPR by 1 | 4     |

| CMPD1  | Rw, mem      | Compare direct word memory to direct GPR and decrement GPR by 1  | 4     |

| CMPD2  | Rw, #data4   | Compare immediate word data to direct GPR and decrement GPR by 2 | 2     |

| CMPD2  | Rw, #data16  | Compare immediate word data to direct GPR and decrement GPR by 2 | 4     |

| CMPD2  | Rw, mem      | Compare direct word memory to direct GPR and decrement GPR by 2  | 4     |

| CMPI1  | Rw, #data4   | Compare immediate word data to direct GPR and increment GPR by 1 | 2     |

| CMPI1  | Rw, #data16  | Compare immediate word data to direct GPR and increment GPR by 1 | 4     |

| CMPI1  | Rw, mem      | Compare direct word memory to direct GPR and increment GPR by 1  | 4     |

| CMPI2  | Rw, #data4   | Compare immediate word data to direct GPR and increment GPR by 2 | 2     |

| CMPI2  | Rw, #data16  | Compare immediate word data to direct GPR and increment GPR by 2 | 4     |

| CMPI2  | Rw, mem      | Compare direct word memory to direct GPR and increment GPR by 2  | 4     |

#### **Shift and Rotate Instructions**

| SHL | Rw, Rw     | Shift left direct word GPR; number of shift cycles specified by direct GPR        | 2 |

|-----|------------|-----------------------------------------------------------------------------------|---|

| SHL | Rw, #data4 | Shift left direct word GPR;<br>number of shift cycles specified by immediate data | 2 |

| SHR | Rw, Rw     | Shift right direct word GPR; number of shift cycles specified by direct GPR       | 2 |

# Table 4 Instruction Set Summary (cont'd)

| Mnemo                                  | onic       | Description                                                                                           | Bytes |  |

|----------------------------------------|------------|-------------------------------------------------------------------------------------------------------|-------|--|

| Shift and Rotate Instructions (cont'd) |            |                                                                                                       |       |  |

| SHR                                    | Rw, #data4 | Shift right direct word GPR; number of shift cycles specified by immediate data                       | 2     |  |

| ROL                                    | Rw, Rw     | Rotate left direct word GPR;<br>number of shift cycles specified by direct GPR                        | 2     |  |

| ROL                                    | Rw, #data4 | Rotate left direct word GPR; number of shift cycles specified by immediate data                       | 2     |  |

| ROR                                    | Rw, Rw     | Rotate right direct word GPR; number of shift cycles specified by direct GPR                          | 2     |  |

| ROR                                    | Rw, #data4 | Rotate right direct word GPR; number of shift cycles specified by immediate data                      | 2     |  |

| ASHR                                   | Rw, Rw     | Arithmetic (sign bit) shift right direct word GPR; number of shift cycles specified by direct GPR     | 2     |  |

| ASHR                                   | Rw, #data4 | Arithmetic (sign bit) shift right direct word GPR; number of shift cycles specified by immediate data | 2     |  |

#### **Data Movement**

| MOV | Rw, Rw       | Move direct word GPR to direct GPR                                                       | 2 |

|-----|--------------|------------------------------------------------------------------------------------------|---|

| MOV | Rw, #data4   | Move immediate word data to direct GPR                                                   | 2 |

| MOV | reg, #data16 | Move immediate word data to direct register                                              | 4 |

| MOV | Rw, [Rw]     | Move indirect word memory to direct GPR                                                  | 2 |

| MOV | Rw, [Rw+]    | Move indirect word memory to direct GPR and post-increment source pointer by 2           | 2 |

| MOV | [Rw], Rw     | Move direct word GPR to indirect memory                                                  | 2 |

| MOV | [-Rw], Rw    | Pre-decrement destination pointer by 2 and move direct word GPR to indirect memory       | 2 |

| MOV | [Rw], [Rw]   | Move indirect word memory to indirect memory                                             | 2 |

| MOV | [Rw+], [Rw]  | Move indirect word memory to indirect memory and post-increment destination pointer by 2 | 2 |

| MOV | [Rw], [Rw+]  | Move indirect word memory to indirect memory and post-increment source pointer by 2      | 2 |

# Table 4 Instruction Set Summary (cont'd)

| Mnemo   | nic                    | Description                                                                              | Bytes |  |  |

|---------|------------------------|------------------------------------------------------------------------------------------|-------|--|--|

| Data Mo | Data Movement (cont'd) |                                                                                          |       |  |  |

| MOV     | Rw,<br>[Rw + #d16]     | Move indirect word memory by base plus constant to direct word GPR                       | 4     |  |  |

| MOV     | [Rw + #d16],<br>Rw     | Move direct word GPR to indirect memory by base plus constant                            | 4     |  |  |

| MOV     | [Rw], mem              | Move direct word memory to indirect memory                                               | 4     |  |  |

| MOV     | mem, [Rw]              | Move indirect word memory to direct memory                                               | 4     |  |  |

| MOV     | reg, mem               | Move direct word memory to direct register                                               | 4     |  |  |

| MOV     | mem, reg               | Move direct word register to direct memory                                               | 4     |  |  |

| MOVB    | Rb, Rb                 | Move direct byte GPR to direct GPR                                                       | 2     |  |  |

| MOVB    | Rb, #data4             | Move immediate byte data to direct GPR                                                   | 2     |  |  |

| MOVB    | reg, #data8            | Move immediate byte data to direct register                                              | 4     |  |  |

| MOVB    | Rb, [Rw]               | Move indirect byte memory to direct GPR                                                  | 2     |  |  |

| MOVB    | Rb, [Rw+]              | Move indirect byte memory to direct GPR and post-increment source pointer by 1           | 2     |  |  |

| MOVB    | [Rw], Rb               | Move direct byte GPR to indirect memory                                                  | 2     |  |  |

| MOVB    | [-Rw], Rb              | Pre-decrement destination pointer by 1 and move direct byte GPR to indirect memory       | 2     |  |  |

| MOVB    | [Rw], [Rw]             | Move indirect byte memory to indirect memory                                             | 2     |  |  |

| MOVB    | [Rw+], [Rw]            | Move indirect byte memory to indirect memory and post-increment destination pointer by 1 | 2     |  |  |

| MOVB    | [Rw], [Rw+]            | Move indirect byte memory to indirect memory and post-increment source pointer by 1      | 2     |  |  |

| MOVB    | Rb,<br>[Rw + #d16]     | Move indirect byte memory by base plus constant to direct byte GPR                       | 4     |  |  |

| MOVB    | [Rw + #d16],<br>Rb     | Move direct byte GPR to indirect memory by base plus constant                            | 4     |  |  |

| MOVB    | [Rw], mem              | Move direct byte memory to indirect memory                                               | 4     |  |  |

| MOVB    | mem, [Rw]              | Move indirect byte memory to direct memory                                               | 4     |  |  |

| MOVB    | reg, mem               | Move direct byte memory to direct register                                               | 4     |  |  |

| MOVB    | mem, reg               | Move direct byte register to direct memory                                               | 4     |  |  |

#### Table 4 Instruction Set Summary (cont'd)

| Mnemonic           | Description                                                         | Bytes |

|--------------------|---------------------------------------------------------------------|-------|

| Data Movement (con | t'd)                                                                |       |

| MOVBS Rw, Rb       | Move direct byte GPR with sign extension to direct word GPR         | 2     |

| MOVBS reg, mem     | Move direct byte memory with sign extension to direct word register | 4     |

| MOVBS mem, reg     | Move direct byte register with sign extension to direct word memory | 4     |

| MOVBZ Rw, Rb       | Move direct byte GPR with zero extension to direct word GPR         | 2     |

| MOVBZ reg, mem     | Move direct byte memory with zero extension to direct word register | 4     |

| MOVBZ mem, reg     | Move direct byte register with zero extension to direct word memory | 4     |

## **Jump and Call Instructions**

| JMPA  | cc, caddr  | Jump absolute if condition is met                                        | 4 |

|-------|------------|--------------------------------------------------------------------------|---|

| JMPI  | cc, [Rw]   | Jump indirect if condition is met                                        | 2 |

| JMPR  | cc, rel    | Jump relative if condition is met                                        | 2 |

| JMPS  | seg, caddr | Jump absolute to a code segment                                          | 4 |

| JB    | baddr, rel | Jump relative if direct bit is set                                       | 4 |

| JBC   | baddr, rel | Jump relative and clear bit if direct bit is set                         | 4 |

| JNB   | baddr, rel | Jump relative if direct bit is not set                                   | 4 |

| JNBS  | baddr, rel | Jump relative and set bit if direct bit is not set                       | 4 |

| CALLA | cc, caddr  | Call absolute subroutine if condition is met                             | 4 |

| CALLI | cc, [Rw]   | Call indirect subroutine if condition is met                             | 2 |

| CALLR | rel        | Call relative subroutine                                                 | 2 |

| CALLS | seg, caddr | Call absolute subroutine in any code segment                             | 4 |

| PCALL | reg, caddr | Push direct word register onto system stack and call absolute subroutine | 4 |

| TRAP  | #trap7     | Call interrupt service routine via immediate trap number                 | 2 |

#### Table 4 Instruction Set Summary (cont'd)

| Mnemonic | Description | Bytes |

|----------|-------------|-------|

|          |             |       |

#### **Return Instructions**

| RET  |     | Return from intra-segment subroutine                                                | 2 |

|------|-----|-------------------------------------------------------------------------------------|---|

| RETS |     | Return from inter-segment subroutine                                                | 2 |

| RETP | reg | Return from intra-segment subroutine and pop direct word register from system stack | 2 |

| RETI |     | Return from interrupt service subroutine                                            | 2 |

# System Control<sup>1)</sup>

| SRST   |                    | Software Reset                                     | 4   |  |  |

|--------|--------------------|----------------------------------------------------|-----|--|--|

| IDLE   |                    | Enter Idle Mode                                    | 4   |  |  |

| PWRDN  |                    | Enter Power Down Mode (supposes NMI-pin being low) | 4   |  |  |

| SRVWD  | Т                  | Service Watchdog Timer                             | 4   |  |  |

| DISWDT | _                  | Disable Watchdog Timer                             | 4   |  |  |

| EINIT  |                    | Signify End-of-Initialization on RSTOUT-pin        | 4 4 |  |  |

| ATOMIC | #irang2            | Begin ATOMIC sequence                              | 2   |  |  |

| EXTR   | #irang2            | Begin EXTended Register sequence                   | 2   |  |  |

| EXTP   | Rw, #irang2        | Begin EXTended Page sequence                       | 2   |  |  |

| EXTP   | #pag10,<br>#irang2 | Begin EXTended Page sequence                       | 4   |  |  |

| EXTPR  | Rw, #irang2        | Begin EXTended Page and Register sequence          | 2   |  |  |

| EXTPR  | #pag10,<br>#irang2 | Begin EXTended Page and Register sequence          | 4   |  |  |

| EXTS   | Rw, #irang2        | Begin EXTended Segment sequence                    | 2   |  |  |

| EXTS   | #seg8,<br>#irang2  | Begin EXTended Segment sequence                    | 4   |  |  |

| EXTSR  | Rw, #irang2        | Begin EXTended Segment and Register sequence       | 2   |  |  |

| EXTSR  | #seg8,<br>#irang2  | Begin EXTended Segment and Register sequence       | 4   |  |  |

#### Table 4 Instruction Set Summary (cont'd)

| Mnemonic | Description | Bytes |

|----------|-------------|-------|

|          |             |       |

#### **System Stack Instructions**

| POP  | reg          | Pop direct word register from system stack                                          | 2 |

|------|--------------|-------------------------------------------------------------------------------------|---|

| PUSH | reg          | Push direct word register onto system stack                                         | 2 |

| SCXT | reg, #data16 | Push direct word register onto system stack and update register with immediate data | 4 |

| SCXT | reg, mem     | Push direct word register onto system stack and update register with direct memory  | 4 |

#### **Miscellaneous**

| NOP | Null operation | 2 |

|-----|----------------|---|

<sup>1)</sup> The ATOMIC and EXTended instructions are not available in the SAB 8XC166(W) devices.

## 4 Encoding

The following pages list the instructions of the 16-bit microcontrollers ordered by their hexadecimal opcodes. This helps to identify specific instructions when reading executable code, i.e. during the debugging phase.

The explanations below should help to read the tables on the following pages:

#### **Extended Opcodes**

These instructions (ADD[C][B], SUB[C][B], CMP[B], AND[B], [X]OR[B]) are encoded by means of additional bits (1/2) in the operand field of the instruction. For these instructions only the lowest four GPRs, R0 to R3, can be used as indirect address pointers.

nnnn.0## $_B$ : Rw $_n$ , #data3 or Rb $_n$ , #data3 nnnn.10ii $_B$ : Rw $_n$ , [Rw $_i$ ] or Rb $_n$ , [Rw $_i$ ] nnnn.11ii $_B$ : Rw $_n$ , [Rw $_i$ +] or Rb $_n$ , [Rw $_i$ +]

2) The following instructions are encoded by means of two additional bits in the operand field of the instruction.

Note: The ATOMIC and EXTended instructions are not available in the SAB 8XC166(W) devices.

00xx.xxxx<sub>B</sub>: EXTS or ATOMIC

$01xx.xxxx_R$ : EXTP

10xx.xxxx<sub>R</sub>: EXTSR or EXTR

11xx.xxxx<sub>B</sub>: EXTPR

#### **Conditional JMPR Instructions**

The condition code to be tested for the JMPR instructions is specified by the opcode. Two mnemonic representation alternatives exist for some of the condition codes (condition codes are described in **Table 5**).

#### **BCLR and BSET Instructions**

The position of the bit to be set or to be cleared is specified by the opcode. The operand 'bitoff.n' (n = 0 to 15) refers to a particular bit within a bit-addressable word.

#### **Undefined Opcodes**

A hardware trap occurs when one of the undefined opcodes signified by '-' is decoded by the CPU.

Note: The 8XC166(W) devices also do not recognize ATOMIC and EXTended instructions, but rather decode an undefined opcode.

| Нех | Bytes | Mnemonic           | Operands                                   | Hex | Bytes | Mnemonic            | Operands                                   |

|-----|-------|--------------------|--------------------------------------------|-----|-------|---------------------|--------------------------------------------|

| 00  | 2     | ADD                | Rw, Rw                                     | 10  | 2     | ADDC                | Rw, Rw                                     |

| 01  | 2     | ADDB               | Rb, Rb                                     | 11  | 2     | ADDCB               | Rb, Rb                                     |

| 02  | 4     | ADD                | reg, mem                                   | 12  | 4     | ADDC                | reg, mem                                   |

| 03  | 4     | ADDB               | reg, mem                                   | 13  | 4     | ADDCB               | reg, mem                                   |

| 04  | 4     | ADD                | mem, reg                                   | 14  | 4     | ADDC                | mem, reg                                   |

| 05  | 4     | ADDB               | mem, reg                                   | 15  | 4     | ADDCB               | mem, reg                                   |

| 06  | 4     | ADD                | reg, #data16                               | 16  | 4     | ADDC                | reg, #data16                               |

| 07  | 4     | ADDB               | reg, #data8                                | 17  | 4     | ADDCB               | reg, #data8                                |

| 08  | 2     | ADD <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 | 18  | 2     | ADDC <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 |

| 09  | 2     | ADDB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 | 19  | 2     | ADDCB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 |

| 0A  | 4     | BFLDL              | bitoff, #mask8,<br>#data8                  | 1A  | 4     | BFLDH               | bitoff, #mask8,<br>#data8                  |

| 0B  | 2     | MUL                | Rw, Rw                                     | 1B  | 2     | MULU                | Rw, Rw                                     |

| 0C  | 2     | ROL                | Rw, Rw                                     | 1C  | 2     | ROL                 | Rw, #data4                                 |

| 0D  | 2     | JMPR               | cc_UC, rel                                 | 1D  | 2     | JMPR                | cc_NET, rel                                |

| 0E  | 2     | BCLR               | bitoff.0                                   | 1E  | 2     | BCLR                | bitoff.1                                   |

| 0F  | 2     | BSET               | bitoff.0                                   | 1F  | 2     | BSET                | bitoff.1                                   |

| Нех | Bytes | Mnemonic           | Operands                                   | Нех | Bytes | Mnemonic            | Operands                                   |

|-----|-------|--------------------|--------------------------------------------|-----|-------|---------------------|--------------------------------------------|

| 20  | 2     | SUB                | Rw, Rw                                     | 30  | 2     | SUBC                | Rw, Rw                                     |

| 21  | 2     | SUBB               | Rb, Rb                                     | 31  | 2     | SUBCB               | Rb, Rb                                     |

| 22  | 4     | SUB                | reg, mem                                   | 32  | 4     | SUBC                | reg, mem                                   |

| 23  | 4     | SUBB               | reg, mem                                   | 33  | 4     | SUBCB               | reg, mem                                   |

| 24  | 4     | SUB                | mem, reg                                   | 34  | 4     | SUBC                | mem, reg                                   |

| 25  | 4     | SUBB               | mem, reg                                   | 35  | 4     | SUBCB               | mem, reg                                   |

| 26  | 4     | SUB                | reg, #data16                               | 36  | 4     | SUBC                | reg, #data16                               |

| 27  | 4     | SUBB               | reg, #data8                                | 37  | 4     | SUBCB               | reg, #data8                                |

| 28  | 2     | SUB <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 | 38  | 2     | SUBC <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 |

| 29  | 2     | SUBB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 | 39  | 2     | SUBCB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 |

| 2A  | 4     | BCMP               | bitaddr, bitaddr                           | ЗА  | 4     | BMOVN               | bitaddr, bitaddr                           |

| 2B  | 2     | PRIOR              | Rw, Rw                                     | 3B  | -     | _                   | _                                          |

| 2C  | 2     | ROR                | Rw, Rw                                     | 3C  | 2     | ROR                 | Rw, #data4                                 |

| 2D  | 2     | JMPR               | cc_EQ, rel or cc_Z, rel                    | 3D  | 2     | JMPR                | cc_NE, rel or cc_NZ, rel                   |

| 2E  | 2     | BCLR               | bitoff.2                                   | 3E  | 2     | BCLR                | bitoff.3                                   |

| 2F  | 2     | BSET               | bitoff.2                                   | 3F  | 2     | BSET                | bitoff.3                                   |

| Нех | Bytes | Mnemonic           | Operands                                   | Нех | Bytes | Mnemonic           | Operands                                   |

|-----|-------|--------------------|--------------------------------------------|-----|-------|--------------------|--------------------------------------------|

| 40  | 2     | CMP                | Rw, Rw                                     | 50  | 2     | XOR                | Rw, Rw                                     |

| 41  | 2     | СМРВ               | Rb, Rb                                     | 51  | 2     | XORB               | Rb, Rb                                     |

| 42  | 4     | CMP                | reg, mem                                   | 52  | 4     | XOR                | reg, mem                                   |

| 43  | 4     | СМРВ               | reg, mem                                   | 53  | 4     | XORB               | reg, mem                                   |

| 44  | _     | _                  | _                                          | 54  | 4     | XOR                | mem, reg                                   |

| 45  | _     | _                  | _                                          | 55  | 4     | XORB               | mem, reg                                   |

| 46  | 4     | CMP                | reg, #data16                               | 56  | 4     | XOR                | reg, #data16                               |

| 47  | 4     | СМРВ               | reg, #data8                                | 57  | 4     | XORB               | reg, #data8                                |

| 48  | 2     | CMP <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 | 58  | 2     | XOR <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 |

| 49  | 2     | CMPB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 | 59  | 2     | XORB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 |

| 4A  | 4     | BMOV               | bitaddr, bitaddr                           | 5A  | 4     | BOR                | bitaddr, bitaddr                           |

| 4B  | 2     | DIV                | Rw                                         | 5B  | 2     | DIVU               | Rw                                         |

| 4C  | 2     | SHL                | Rw, Rw                                     | 5C  | 2     | SHL                | Rw, #data4                                 |

| 4D  | 2     | JMPR               | cc_V, rel                                  | 5D  | 2     | JMPR               | cc_NV, rel                                 |

| 4E  | 2     | BCLR               | bitoff.4                                   | 5E  | 2     | BCLR               | bitoff.5                                   |

| 4F  | 2     | BSET               | bitoff.4                                   | 5F  | 2     | BSET               | bitoff.5                                   |

| Нех | Bytes | Mnemonic           | Operands                                   | Нех | Bytes | Mnemonic          | Operands                                   |

|-----|-------|--------------------|--------------------------------------------|-----|-------|-------------------|--------------------------------------------|

| 60  | 2     | AND                | Rw, Rw                                     | 70  | 2     | OR                | Rw, Rw                                     |

| 61  | 2     | ANDB               | Rb, Rb                                     | 71  | 2     | ORB               | Rb, Rb                                     |

| 62  | 4     | AND                | reg, mem                                   | 72  | 4     | OR                | reg, mem                                   |

| 63  | 4     | ANDB               | reg, mem                                   | 73  | 4     | ORB               | reg, mem                                   |

| 64  | 4     | AND                | mem, reg                                   | 74  | 4     | OR                | mem, reg                                   |

| 65  | 4     | ANDB               | mem, reg                                   | 75  | 4     | ORB               | mem, reg                                   |

| 66  | 4     | AND                | reg, #data16                               | 76  | 4     | OR                | reg, #data16                               |

| 67  | 4     | ANDB               | reg, #data8                                | 77  | 4     | ORB               | reg, #data8                                |

| 68  | 2     | AND <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 | 78  | 2     | OR <sup>1)</sup>  | Rw, [Rw +] or<br>Rw, [Rw] or<br>Rw, #data3 |

| 69  | 2     | ANDB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 | 79  | 2     | ORB <sup>1)</sup> | Rb, [Rw +] or<br>Rb, [Rw] or<br>Rb, #data3 |

| 6A  | 4     | BAND               | bitaddr, bitaddr                           | 7A  | 4     | BXOR              | bitaddr, bitaddr                           |

| 6B  | 2     | DIVL               | Rw                                         | 7B  | 2     | DIVLU             | Rw                                         |

| 6C  | 2     | SHR                | Rw, Rw                                     | 7C  | 2     | SHR               | Rw, #data4                                 |

| 6D  | 2     | JMPR               | cc_N, rel                                  | 7D  | 2     | JMPR              | cc_NN, rel                                 |

| 6E  | 2     | BCLR               | bitoff.6                                   | 7E  | 2     | BCLR              | bitoff.7                                   |

| 6F  | 2     | BSET               | bitoff.6                                   | 7F  | 2     | BSET              | bitoff.7                                   |

| Нех | Bytes | Mnemonic | Operands                    | Нех | Bytes | Mnemonic | Operands                  |

|-----|-------|----------|-----------------------------|-----|-------|----------|---------------------------|

| 80  | 2     | CMPI1    | Rw, #data4                  | 90  | 2     | CMPI2    | Rw, #data4                |

| 81  | 2     | NEG      | Rw                          | 91  | 2     | CPL      | Rw                        |

| 82  | 4     | CMPI1    | Rw, mem                     | 92  | 4     | CMPI2    | Rw, mem                   |

| 83  | _     | _        | _                           | 93  | _     | _        | -                         |

| 84  | 4     | MOV      | [Rw], mem                   | 94  | 4     | MOV      | mem, [Rw]                 |

| 85  | _     | _        | _                           | 95  | _     | _        | _                         |

| 86  | 4     | CMPI1    | Rw, #data16                 | 96  | 4     | CMPI2    | Rw, #data16               |

| 87  | 4     | IDLE     | _                           | 97  | 4     | PWRDN    | _                         |

| 88  | 2     | MOV      | [-Rw], Rw                   | 98  | 2     | MOV      | Rw, [Rw+]                 |

| 89  | 2     | MOVB     | [-Rw], Rb                   | 99  | 2     | MOVB     | Rb, [Rw+]                 |

| 8A  | 4     | JB       | bitaddr, rel                | 9A  | 4     | JNB      | bitaddr, rel              |

| 8B  | _     | _        | _                           | 9B  | 2     | TRAP     | #trap7                    |

| 8C  | _     | _        | _                           | 9C  | 2     | JMPI     | cc, [Rw]                  |

| 8D  | 2     | JMPR     | cc_C, rel or<br>cc_ULT, rel | 9D  | 2     | JMPR     | cc_NC, rel or cc_UGE, rel |

| 8E  | 2     | BCLR     | bitoff.8                    | 9E  | 2     | BCLR     | bitoff.9                  |

| 8F  | 2     | BSET     | bitoff.8                    | 9F  | 2     | BSET     | bitoff.9                  |

| Нех | Bytes | Mnemonic | Operands     | Нех | Bytes | Mnemonic | Operands     |

|-----|-------|----------|--------------|-----|-------|----------|--------------|

| A0  | 2     | CMPD1    | Rw, #data4   | ВО  | 2     | CMPD2    | Rw, #data4   |

| A1  | 2     | NEGB     | Rb           | B1  | 2     | CPLB     | Rb           |

| A2  | 4     | CMPD1    | Rw, mem      | B2  | 4     | CMPD2    | Rw, mem      |

| A3  | _     | _        | _            | ВЗ  | _     | _        | -            |

| A4  | 4     | MOVB     | [Rw], mem    | B4  | 4     | MOVB     | mem, [Rw]    |

| A5  | 4     | DISWDT   | _            | B5  | 4     | EINIT    | _            |

| A6  | 4     | CMPD1    | Rw, #data16  | В6  | 4     | CMPD2    | Rw, #data16  |

| A7  | 4     | SRVWDT   | _            | B7  | 4     | SRST     | _            |

| A8  | 2     | MOV      | Rw, [Rw]     | B8  | 2     | MOV      | [Rw], Rw     |

| A9  | 2     | MOVB     | Rb, [Rw]     | B9  | 2     | MOVB     | [Rw], Rb     |

| AA  | 4     | JBC      | bitaddr, rel | ВА  | 4     | JNBS     | bitaddr, rel |

| AB  | 2     | CALLI    | cc, [Rw]     | BB  | 2     | CALLR    | rel          |

| AC  | 2     | ASHR     | Rw, Rw       | ВС  | 2     | ASHR     | Rw, #data4   |

| AD  | 2     | JMPR     | cc_SGT, rel  | BD  | 2     | JMPR     | cc_SLE, rel  |